# MIPS64® Architecture For Programmers Volume III: The MIPS64® Privileged Resource Architecture

Document Number: MD00091 Revision 2.62 January 02, 2009

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2001-2003,2005,2008-2009 MIPS Technologies Inc. All rights reserved.

Copyright © 2001-2003,2005,2008-2009 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS I, MIPS II, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS-3D, MIPS16, MIPS16e, MIPS32, MIPS64, MIPS-Based, MIPSsim, MIPSpro, MIPS Technologies logo, MIPS-VERIFIED logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 24K, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, R3000, R4000, R5000, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, OCI, PDtrace, the Pipeline, Pro Series, SEAD, SEAD-2, SmartMIPS, SOC-it, System Navigator, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

## **Contents**

| Chapter 1: About This Book                                                                        | 11 |

|---------------------------------------------------------------------------------------------------|----|

| 1.1: Typographical Conventions                                                                    | 11 |

| 1.1.1: Italic Text                                                                                | 11 |

| 1.1.2: Bold Text                                                                                  | 11 |

| 1.1.3: Courier Text                                                                               |    |

| 1.2: UNPREDICTABLE and UNDEFINED                                                                  |    |

| 1.2.1: UNPREDICTABLE                                                                              | 12 |

| 1.2.2: UNDEFINED                                                                                  |    |

| 1.2.3: UNSTABLE                                                                                   |    |

| 1.3: Special Symbols in Pseudocode Notation                                                       |    |

| 1.4: For More Information                                                                         |    |

| Chapter 2: The MIPS64 Privileged Resource Architecture                                            |    |

| 2.1: Introduction                                                                                 |    |

| 2.2: The MIPS Coprocessor Model                                                                   |    |

| 2.2.1: CP0 - The System Coprocessor                                                               |    |

| 2.2.2: CP0 Registers                                                                              | 17 |

| Chapter 3: MIPS64 Operating Modes                                                                 | 19 |

| 3.1: Debug Mode                                                                                   | 19 |

| 3.2: Kernel Mode                                                                                  | 19 |

| 3.3: Supervisor Mode                                                                              | 20 |

| 3.4: User Mode                                                                                    |    |

| 3.5: Other Modes                                                                                  |    |

| 3.5.1: 64-bit Address Enable                                                                      | 20 |

| 3.5.2: 64-bit Operations Enable                                                                   |    |

| 3.5.3: 64-bit Floating Point Operations Enable                                                    |    |

| 3.5.4: 64-bit FPR Enable                                                                          |    |

| 3.5.5: Coprocessor 0 Enable                                                                       |    |

| Chapter 4: Virtual Memory                                                                         | 23 |

| 4.1: Support in Release 1 and Release 2 of the Architecture                                       |    |

| 4.1.1: Virtual Memory                                                                             |    |

| 4.1.2: Physical Memory                                                                            |    |

| 4.2: Terminology                                                                                  |    |

| 4.2.1: Address Space                                                                              |    |

| 4.2.2: Segment and Segment Size (SEGBITS)                                                         |    |

| 4.2.3: Physical Address Size (PABITS)                                                             | 24 |

| 4.2: 3: Virtual Address Spaces                                                                    |    |

|                                                                                                   |    |

| 4.4: Compliance                                                                                   |    |

| 4.5: Access Control as a Function of Address and Operating Mode                                   |    |

| 4.6: Address Translation and Cacheability & Coherency Attributes for the kseg0 and kseg1 Segments |    |

| 4.7: Address Translation and Cacheability and Coherency Attributes for the xkphys Segment         |    |

| 4.8: Address Translation for the kuseg Segment when Status <sub>ERL</sub> = 1                     |    |

| 4.9: Special Behavior for the kseg3 Segment when Debug <sub>DM</sub> = 1                          |    |

| 4.10: Special Behavior for Data References in User Mode with Status IIX = 0                       | 34 |

| 4.11: TLB-Based Virtual Address Translation                             | 35  |

|-------------------------------------------------------------------------|-----|

| 4.11.1: Address Space Identifiers (ASID)                                |     |

| 4.11.2: TLB Organization                                                |     |

| 4.11.3: TLB Initialization                                              |     |

| 4.11.4: Address Translation                                             | 38  |

| Objection E. Intermedia and Engage                                      | 40  |

| Chapter 5: Interrupts and Exceptions                                    |     |

| 5.1: Interrupts                                                         |     |

| 5.1.1: Interrupt Modes                                                  |     |

| 5.1.2: Generation of Exception Vector Offsets for Vectored Interrupts   |     |

| 5.2.1: Exception Priority                                               |     |

| 5.2.2: Exception Vector Locations.                                      |     |

| 5.2.3: General Exception Processing                                     |     |

| 5.2.4: EJTAG Debug Exception                                            |     |

| 5.2.5: Reset Exception                                                  |     |

| 5.2.6: Soft Reset Exception                                             |     |

| 5.2.7: Non Maskable Interrupt (NMI) Exception                           |     |

| 5.2.8: Machine Check Exception                                          |     |

| 5.2.9: Address Error Exception                                          |     |

| 5.2.10: TLB Refill and XTLB Refill Exceptions                           |     |

| 5.2.11: TLB Invalid Exception                                           |     |

| 5.2.12: TLB Modified Exception                                          |     |

| 5.2.13: Cache Error Exception                                           |     |

| 5.2.14: Bus Error Exception                                             |     |

| 5.2.15: Integer Overflow Exception                                      |     |

| 5.2.16: Trap Exception                                                  | 70  |

| 5.2.17: System Call Exception                                           | 70  |

| 5.2.18: Breakpoint Exception                                            | 70  |

| 5.2.19: Reserved Instruction Exception                                  |     |

| 5.2.20: Coprocessor Unusable Exception                                  |     |

| 5.2.21: MDMX Unusable Exception                                         |     |

| 5.2.22: Floating Point Exception                                        |     |

| 5.2.23: Coprocessor 2 Exception                                         |     |

| 5.2.24: Watch Exception                                                 |     |

| 5.2.25: Interrupt Exception                                             | 74  |

| Chapter 6: GPR Shadow Registers                                         | 75  |

| 6.1: Introduction to Shadow Sets                                        |     |

| 6.2: Support Instructions                                               |     |

| Chapter 7: CP0 Hazards                                                  | 77  |

| ·                                                                       |     |

| 7.1: Introduction                                                       |     |

| 7.2: Types of Hazards                                                   |     |

| 7.2.1: Execution Hazards                                                |     |

| 7.2.2. Instruction Hazards 7.3: Hazard Clearing Instructions and Events |     |

| 7.3.1: Instruction Encoding                                             |     |

| Chanten & Commonocon & Benistens                                        | 0.4 |

| Chapter 8: Coprocessor 0 Registers                                      |     |

| 8.2. Notation                                                           | 86  |

| 8.3: Writing CPU Registers                                                                   | 86  |

|----------------------------------------------------------------------------------------------|-----|

| 8.4: Index Register (CP0 Register 0, Select 0)                                               | 88  |

| 8.5: Random Register (CP0 Register 1, Select 0)                                              | 89  |

| 8.6: EntryLo0, EntryLo1 (CP0 Registers 2 and 3, Select 0)                                    | 90  |

| 8.7: Context Register (CP0 Register 4, Select 0)                                             |     |

| 8.8: UserLocal Register (CP0 Register 4, Select 2)                                           |     |

| 8.9: PageMask Register (CP0 Register 5, Select 0)                                            |     |

| 8.10: PageGrain Register (CP0 Register 5, Select 1)                                          |     |

| 8.11: Wired Register (CP0 Register 6, Select 0)                                              |     |

| 8.12: HWREna Register (CP0 Register 7, Select 0)                                             |     |

| 8.13: BadVAddr Register (CP0 Register 8, Select 0)                                           |     |

| 8.14: Count Register (CP0 Register 9, Select 0)                                              |     |

| 8.15: Reserved for Implementations (CP0 Register 9, Selects 6 and 7)                         |     |

| 8.16: EntryHi Register (CP0 Register 10, Select 0)                                           |     |

| 8.17: Compare Register (CP0 Register 11, Select 0)                                           |     |

| 8.18: Reserved for Implementations (CP0 Register 11, Selects 6 and 7)                        |     |

| 8.19: Status Register (CP Register 12, Select 0)                                             |     |

| 8.20: IntCtl Register (CP0 Register 12, Select 1)                                            |     |

| 8.21: SRSCtl Register (CP0 Register 12, Select 2)                                            |     |

| 8.22: SRSMap Register (CP0 Register 12, Select 3)                                            |     |

| 8.23: Cause Register (CP0 Register 13, Select 0)                                             |     |

| 8.24: Exception Program Counter (CP0 Register 14, Select 0)                                  |     |

| 8.24.1: Special Handling of the EPC Register in Processors That Implement the MIPS16e ASE    |     |

| 8.25: Processor Identification (CP0 Register 15, Select 0)                                   |     |

| 8.26: EBase Register (CP0 Register 15, Select 1)                                             |     |

| 8.27: Configuration Register (CP0 Register 16, Select 0)                                     |     |

| 8.28: Configuration Register 1 (CP0 Register 16, Select 1)                                   |     |

| 8.29: Configuration Register 2 (CP0 Register 16, Select 2)                                   |     |

| 8.30: Configuration Register 3 (CP0 Register 16, Select 3)                                   |     |

| 8.31: Reserved for Implementations (CP0 Register 16, Selects 6 and 7)                        |     |

| 8.32: Load Linked Address (CP0 Register 17, Select 0)                                        |     |

| 8.33: WatchLo Register (CP0 Register 18)                                                     |     |

| 8.34: WatchHi Register (CP0 Register 19)                                                     |     |

| 8.35: XContext Register (CP0 Register 20, Select 0)                                          |     |

| 8.36: Reserved for Implementations (CP0 Register 22, all Select values)                      |     |

| 8.37: Debug Register (CP0 Register 23)                                                       |     |

| 8.38: DEPC Register (CP0 Register 24)                                                        |     |

| 8.38.1: Special Handling of the DEPC Register in Processors That Implement the MIPS16e ASE   |     |

| 8.39: Performance Counter Register (CP0 Register 25)                                         |     |

| 8.40: ErrCtl Register (CP0 Register 26, Select 0)                                            |     |

| 8.41: CacheErr Register (CP0 Register 27, Select 0)                                          |     |

| 8.42: TagLo Register (CP0 Register 28, Select 0, 2)                                          |     |

| 8.43: DataLo Register (CP0 Register 28, Select 1, 3)                                         |     |

| 8.44: TagHi Register (CP0 Register 29, Select 0, 2)                                          |     |

| 8.45: DataHi Register (CP0 Register 29, Select 1, 3)                                         |     |

| 8.46: ErrorEPC (CP0 Register 30, Select 0)                                                   |     |

| 8.46.1: Special Handling of the ErrorEPC Register in Processors That Implement the MIPS16e A |     |

| 8.47: DESAVE Register (CP0 Register 31)                                                      |     |

| Appendix A: Alternative MMU Organizations                                                    | 175 |

| A.1: Fixed Mapping MMU                                                                       |     |

| A.1.1: Fixed Address Translation                                                             |     |

| A.1.2: Cacheability Attributes                                                               |     |

| Appendix B: Revision History                 | 183 |

|----------------------------------------------|-----|

| A.2.3: Changes to the CP0 Register Interface | 181 |

| A.2.2: Address Translation                   | 180 |

| A.2.1: BAT Organization                      | 179 |

| A.2: Block Address Translation               | 179 |

| A.1.3: Changes to the CP0 Register Interface |     |

## **Figures**

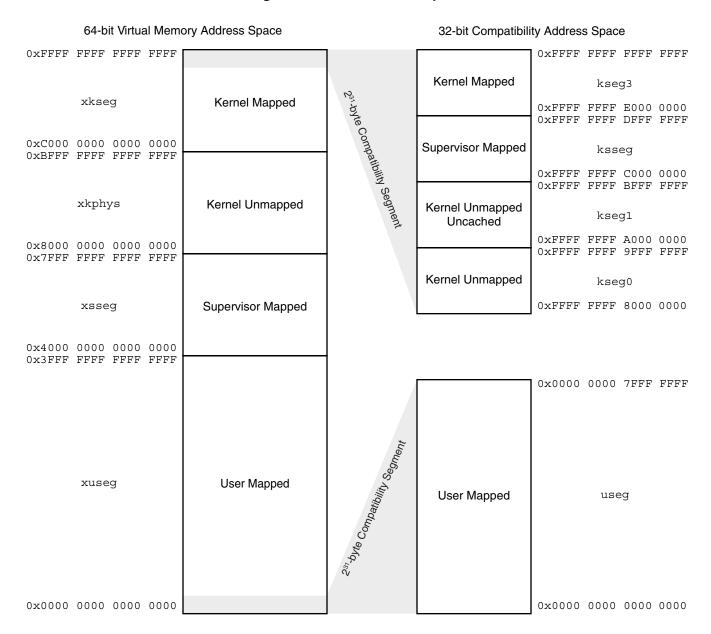

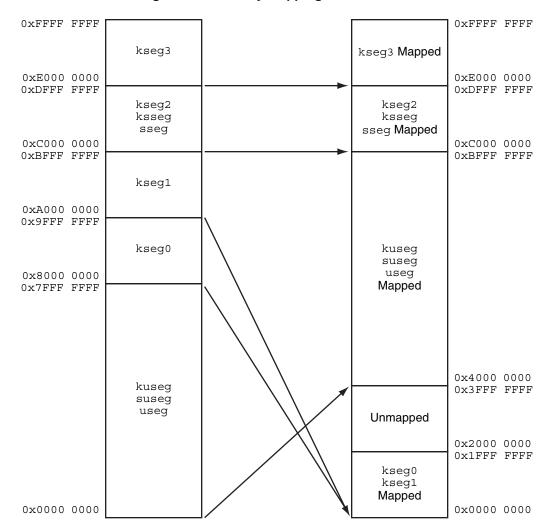

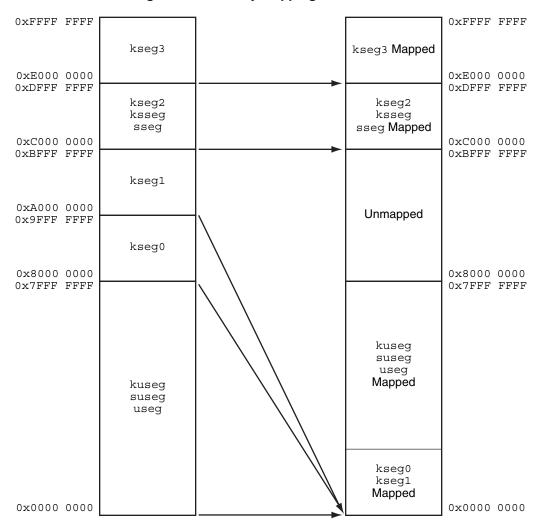

| Figure 4-1: Virtual Address Space                                                 |     |

|-----------------------------------------------------------------------------------|-----|

| Figure 4-2: Address Interpretation for the xkphys Segment                         | 31  |

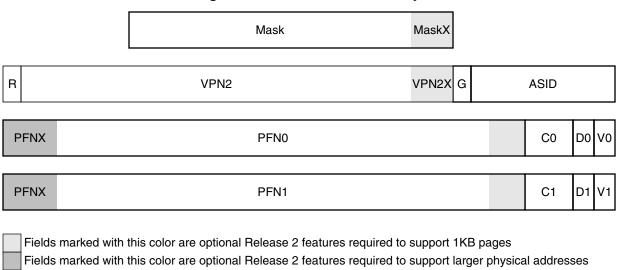

| Figure 4-3: Contents of a TLB Entry                                               | 36  |

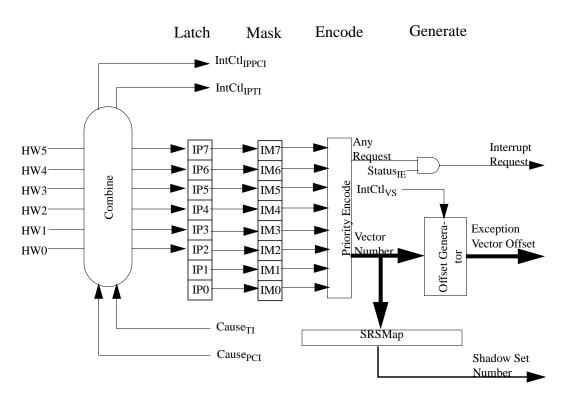

| Figure 5-1: Interrupt Generation for Vectored Interrupt Mode                      | 49  |

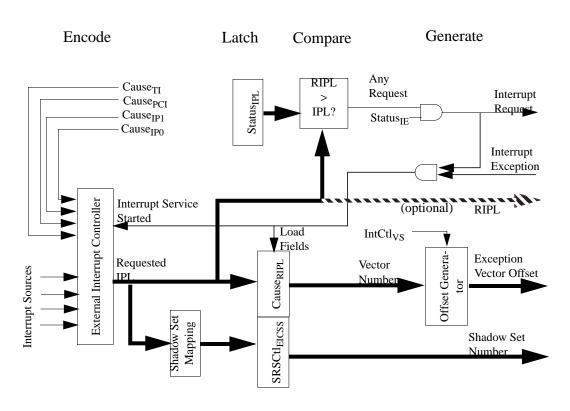

| Figure 5-2: Interrupt Generation for External Interrupt Controller Interrupt Mode | 52  |

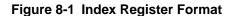

| Figure 8-1: Index Register Format                                                 | 88  |

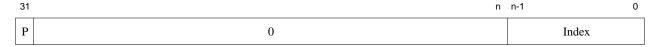

| Figure 8-2: Random Register Format                                                |     |

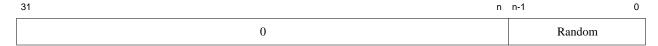

| Figure 8-3: EntryLo0, EntryLo1 Register Format in Release 1 of the Architecture   |     |

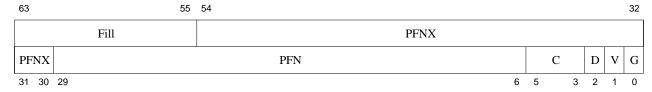

| Figure 8-4: EntryLo0, EntryLo1 Register Format in Release 2 of the Architecture   |     |

| Figure 8-5: Context Register Format                                               |     |

| Figure 8-6: UserLocal Register Format                                             |     |

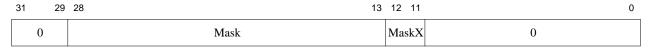

| Figure 8-7: PageMask Register Format                                              | 98  |

| Figure 8-8: PageGrain Register Format                                             |     |

| Figure 8-9: Wired And Random Entries In The TLB                                   |     |

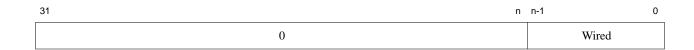

| Figure 8-10: Wired Register Format                                                |     |

| Figure 8-11: HWREna Register Format                                               | 104 |

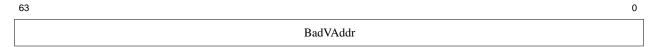

| Figure 8-12: BadVAddr Register Format                                             |     |

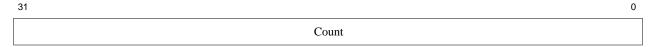

| Figure 8-13: Count Register Format                                                |     |

| Figure 8-14: EntryHi Register Format                                              |     |

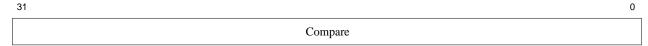

| Figure 8-15: Compare Register Format                                              |     |

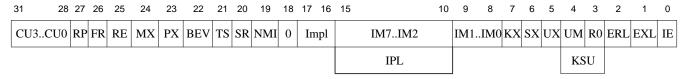

| Figure 8-16: Status Register Format                                               |     |

| Figure 8-17: IntCtl Register Format                                               |     |

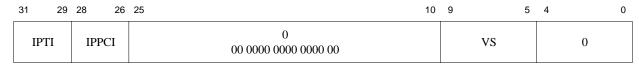

| Figure 8-18: SRSCtl Register Format                                               |     |

| Figure 8-19: SRSMap Register Format                                               |     |

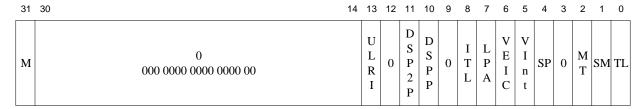

| Figure 8-20: Cause Register Format                                                |     |

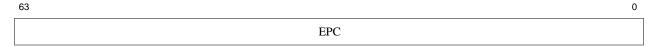

| Figure 8-21: EPC Register Format                                                  |     |

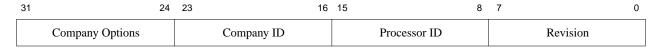

| Figure 8-22: PRId Register Format                                                 |     |

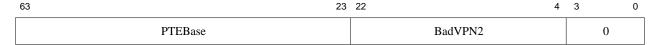

| Figure 8-23: EBase Register Format                                                |     |

| Figure 8-24: Config Register Format                                               |     |

| Figure 8-25: Config1 Register Format                                              |     |

| Figure 8-26: Config2 Register Format                                              |     |

| Figure 8-27: Config3 Register Format                                              |     |

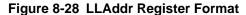

| Figure 8-28: LLAddr Register Format                                               |     |

| Figure 8-29: WatchLo Register Format                                              |     |

| Figure 8-30: WatchHi Register Format                                              | 154 |

| Figure 8-31: XContext Register Format                                             |     |

| Figure 8-32: Performance Counter Control Register Format                          |     |

| Figure 8-33: Performance Counter Counter Register Format                          |     |

| Figure 8-34: ErrorEPC Register Format                                             |     |

| Figure A-1: Memory Mapping when ERL = 0                                           |     |

| Figure A-2: Memory Mapping when ERL = 1                                           |     |

| Figure A-3: Config Register Additions                                             | 179 |

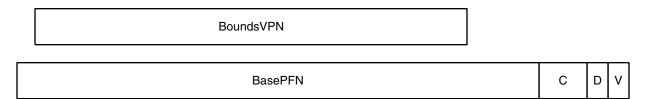

| Figure A-4: Contents of a BAT Entry                                               | 180 |

## **Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                                               | 13  |

|-----------------------------------------------------------------------------------------------------------|-----|

| Table 4.1: Virtual Memory Address Spaces                                                                  |     |

| Table 4.2: Address Space Access and TLB Refill Selection as a Function of Operating Mode                  | 28  |

| Table 4.3: Address Translation and Cacheability and Coherency Attributes for the kseg0 and kseg1 Segments |     |

| Table 4.4: Address Translation and Cacheability Attributes for the xkphys Segment                         | 31  |

| Table 4.5: Physical Address Generation                                                                    | 41  |

| Table 5.1: Interrupt Modes                                                                                | 44  |

| Table 5.2: Request for Interrupt Service in Interrupt Compatibility Mode                                  | 45  |

| Table 5.3: Relative Interrupt Priority for Vectored Interrupt Mode                                        | 48  |

| Table 5.4: Exception Vector Offsets for Vectored Interrupts                                               | 53  |

| Table 5.5: Interrupt State Changes Made Visible by EHB                                                    | 54  |

| Table 5.6: Priority of Exceptions                                                                         |     |

| Table 5.7: Exception Type Characteristics                                                                 | 56  |

| Table 5.8: Exception Vector Base Addresses                                                                |     |

| Table 5.9: Exception Vector Offsets                                                                       |     |

| Table 5.10: Exception Vectors                                                                             |     |

| Table 5.11: Value Stored in EPC, ErrorEPC, or DEPC on an Exception                                        |     |

| Table 6.1: Instructions Supporting Shadow Sets                                                            |     |

| Table 7.1: Execution Hazards                                                                              |     |

| Table 7.2: Instruction Hazards                                                                            |     |

| Table 7.3: Hazard Clearing Instructions                                                                   | 80  |

| Table 8.1: Coprocessor 0 Registers in Numerical Order                                                     |     |

| Table 8.2: Read/Write Bit Field Notation                                                                  |     |

| Table 8.3: Index Register Field Descriptions                                                              |     |

| Table 8.4: Random Register Field Descriptions                                                             |     |

| Table 8.5: EntryLo0, EntryLo1 Register Field Descriptions in Release 1 of the Architecture                |     |

| Table 8.6: EntryLo0, EntryLo1 Register Field Descriptions in Release 2 of the Architecture                |     |

| Table 8.7: EntryLo Field Widths as a Function of PABITS                                                   |     |

| Table 8.8: Cacheability and Coherency Attributes                                                          |     |

| Table 8.9: Context Register Field Descriptions                                                            |     |

| Table 8.10: UserLocal Register Field Descriptions                                                         | 97  |

| Table 8.11: PageMask Register Field Descriptions                                                          | 98  |

| Table 8.12: Values for the Mask and MaskX <sup>1</sup> Fields of the PageMask Register                    |     |

| Table 8.13: PageGrain Register Field Descriptions                                                         | 100 |

| Table 8.14: Wired Register Field Descriptions                                                             |     |

| Table 8.15: HWREna Register Field Descriptions                                                            |     |

| Table 8.16: RDHWR Register Numbers                                                                        |     |

| Table 8.17: BadVAddr Register Field Descriptions                                                          |     |

| Table 8.18: Count Register Field Descriptions.                                                            |     |

| Table 8.19: EntryHi Register Field Descriptions                                                           |     |

| Table 8.20: Compare Register Field Descriptions                                                           |     |

| Table 8.21: Status Register Field Descriptions                                                            |     |

| Table 8.22: IntCtl Register Field Descriptions                                                            |     |

| Table 8.23: SRSCtl Register Field Descriptions                                                            |     |

| Table 8.24: Sources for new SRSCtl <sub>CSS</sub> on an Exception or Interrupt                            |     |

| Table 8.25: SRSMap Register Field Descriptions                                                            |     |

| Table 8.26: Cause Register Field Descriptions                                                             | 127 |

| Table 8.27: Cause Register ExcCode Field                                  | 130 |

|---------------------------------------------------------------------------|-----|

| Table 8.28: EPC Register Field Descriptions                               | 132 |

| Table 8.29: PRId Register Field Descriptions                              | 134 |

| Table 8.30: EBase Register Field Descriptions                             | 136 |

| Table 8.31: Conditions Under Which EBase1512 Must Be Zero                 | 137 |

| Table 8.32: Config Register Field Descriptions                            | 138 |

| Table 8.33: Config1 Register Field Descriptions                           |     |

| Table 8.34: Config2 Register Field Descriptions                           |     |

| Table 8.35: Config3 Register Field Descriptions                           | 147 |

| Table 8.36: LLAddr Register Field Descriptions                            | 151 |

| Table 8.37: WatchLo Register Field Descriptions                           | 152 |

| Table 8.38: WatchHi Register Field Descriptions                           | 154 |

| Table 8.39: XContext Register Fields                                      | 156 |

| Table 8.40: Example Performance Counter Usage of the PerfCnt CP0 Register |     |

| Table 8.41: Performance Counter Control Register Field Descriptions       | 162 |

| Table 8.42: Performance Counter Counter Register Field Descriptions       | 165 |

| Table 8.43: ErrorEPC Register Field Descriptions                          | 172 |

| Table A.1: Physical Address Generation from Virtual Addresses             | 175 |

| Table A.2: Config Register Field Descriptions                             |     |

| Table A.3: BAT Entry Assignments                                          |     |

|                                                                           |     |

10

## **About This Book**

The MIPS64® Architecture For Programmers Volume III: The MIPS64® Privileged Resource Architecture comes as a multi-volume set.

- Volume I describes conventions used throughout the document set, and provides an introduction to the MIPS64®

Architecture

- Volume II provides detailed descriptions of each instruction in the MIPS64® instruction set

- Volume III describes the MIPS64® Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS64® processor implementation

- Volume IV-a describes the MIPS16e<sup>™</sup> Application-Specific Extension to the MIPS64® Architecture

- Volume IV-b describes the MDMX<sup>TM</sup> Application-Specific Extension to the MIPS64® Architecture

- Volume IV-c describes the MIPS-3D® Application-Specific Extension to the MIPS64® Architecture

- Volume IV-d describes the SmartMIPS®Application-Specific Extension to the MIPS32® Architecture and is not applicable to the MIPS64® document set

## 1.1 Typographical Conventions

This section describes the use of *italic*, **bold** and courier fonts in this book.

#### 1.1.1 Italic Text

- is used for *emphasis*

- is used for *bits*, *fields*, *registers*, that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S*, *D*, and *PS*

- is used for the memory access types, such as cached and uncached

#### 1.1.2 Bold Text

- represents a term that is being defined

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through

- is used to emphasize **UNPREDICTABLE** and **UNDEFINED** behavior, as defined below.

#### 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

#### 1.2 UNPREDICTABLE and UNDEFINED

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CPO usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

#### 1.2.1 UNPREDICTABLE

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

- Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which

is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user

mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in

another process

- UNPREDICTABLE operations must not halt or hang the processor

#### 1.2.2 UNDEFINED

12

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

**UNDEFINED** operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

#### 1.2.3 UNSTABLE

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

**UNSTABLE** values have one implementation restriction:

• Implementations of operations generating **UNSTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

## 1.3 Special Symbols in Pseudocode Notation

In this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

**Table 1.1 Symbols Used in Instruction Operation Statements**

| Symbol          | Meaning                                                                                                                                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>←</b>        | Assignment                                                                                                                                                                                                                                                                  |

| =, ≠            | Tests for equality and inequality                                                                                                                                                                                                                                           |

| I               | Bit string concatenation                                                                                                                                                                                                                                                    |

| x <sup>y</sup>  | A y-bit string formed by y copies of the single-bit value x                                                                                                                                                                                                                 |

| b#n             | A constant value <i>n</i> in base <i>b</i> . For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. |

| 0bn             | A constant value <i>n</i> in base 2. For instance 0b100 represents the binary value 100 (decimal 4).                                                                                                                                                                        |

| 0xn             | A constant value <i>n</i> in base 16. For instance 0x100 represents the hexadecimal value 100 (decimal 256).                                                                                                                                                                |

| x <sub>yz</sub> | Selection of bits y through z of bit string x. Little-endian bit notation (rightmost bit is 0) is used. If y is less than z, this expression is an empty (zero length) bit string.                                                                                          |

| +, -            | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                                          |

| *,×             | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                                      |

| div             | 2's complement integer division                                                                                                                                                                                                                                             |

| mod             | 2's complement modulo                                                                                                                                                                                                                                                       |

| /               | Floating point division                                                                                                                                                                                                                                                     |

| <               | 2's complement less-than comparison                                                                                                                                                                                                                                         |

| >               | 2's complement greater-than comparison                                                                                                                                                                                                                                      |

| ≤               | 2's complement less-than or equal comparison                                                                                                                                                                                                                                |

| ≥               | 2's complement greater-than or equal comparison                                                                                                                                                                                                                             |

| nor             | Bitwise logical NOR                                                                                                                                                                                                                                                         |

| xor             | Bitwise logical XOR                                                                                                                                                                                                                                                         |

| and             | Bitwise logical AND                                                                                                                                                                                                                                                         |

| or              | Bitwise logical OR                                                                                                                                                                                                                                                          |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPRLEN               | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPR[x]               | CPU general-purpose register $x$ . The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SGPR[s,x]            | In Release 2 of the Architecture, multiple copies of the CPU general-purpose registers may be implemented. $SGPR[s,x]$ refers to GPR set s, register x.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FPR[x]               | Floating Point operand register x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FCC[CC]              | Floating Point condition code CC. FCC[0] has the same value as COC[1].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FPR[x]               | Floating Point (Coprocessor unit 1), general register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CPR[z,x,s]           | Coprocessor unit z, general register x, select s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CP2CPR[x]            | Coprocessor unit 2, general register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CCR[z,x]             | Coprocessor unit z, control register x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CP2CCR[x]            | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| COC[z]               | Coprocessor unit z condition signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Xlat[x]              | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BigEndianMem         | Endian mode as configured at chip reset (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions), and the endianness of Kernel and Supervisor mode execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BigEndianCPU         | The endianness for load and store instructions (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ReverseEndian        | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only, and is implemented by setting the $RE$ bit of the $Status$ register. Thus, ReverseEndian may be computed as $(SR_{RE}$ and User mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LLbit                | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs and is tested by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| I:,<br>I+n:,<br>I-n: | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time of another instruction. When this happens, the instruction operation is written in sections labeled with the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction may have a result that is not available until after the next instruction. Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled <b>I+1</b> .  The effect of pseudocode statements for the current instruction labelled <b>I+1</b> appears to occur "at the same time" as the effect of pseudocode statements labeled <b>I</b> for the following instruction. Within one pseudocode sequence, the effects of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections. |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol                               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PC                                   | tion word. The address of the instruction that occurs during the next instruction time is deting a value to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction pseudocode statement, it is automatically incremented by either 2 (in the case of a 16-bit 1 tion) or 4 before the next instruction time. A taken branch assigns the target address to the instruction time of the instruction in the branch delay slot.  In the MIPS Architecture, the PC value is only visible indirectly, such as when the processe address into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocess |                                                                                                                                                                                                                                                                     |                                                                                                 | e MIPS Architecture, the PC value is only visible indirectly, such as when the processor stores the restart ess into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an option. The PC value contains a full 64-bit address all of which are significant during a memory reference. |  |  |  |  |  |

| ISA Mode                             | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                                                                                                                                                                                                                                                   | MIPS16e Application Specific Extension, the ISA Mode de the processor is executing, as follows: | e is a single-bit reg-                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |